固态变压器(SST)研发全栈解析:从SiC器件选型到多物理场仿真——电力电子工程师的软硬件装备指南

时间:2026-03-18 22:12:13

来源:UltraLAB图形工作站方案网站

人气:58

作者:管理员

高压高频绝缘设计、模块化冗余控制、电磁-热-力耦合仿真——破解SST三大生死坎的算力配置方案

当英伟达GB300强制要求采用SST供电,当特斯拉兆瓦超充站全面淘汰工频变压器,固态变压器(SST)已从实验室概念跃升为万亿级赛道的核心硬通货。然而,这款被誉为"能源互联网入口"的产品,其研发门槛极高——90%的入局者都倒在了高压SiC可靠性验证、高频绝缘失效、模块化控制算法这三道"生死坎"上。

设计一台10kV/6MW级别的SST,需要跨越电力电子、材料科学、电磁场、热力学、控制论的学科壁垒。本文深度拆解SST研发的技术全栈,并给出支撑这一复杂系统工程的高性能算力配置方案。

一、SST设计的技术全景图:五大核心领域

固态变压器不是传统变压器的简单升级,而是基于第三代半导体的"电能智能路由系统"。其研发涉及五大关键技术领域:

1. 功率半导体器件选型与驱动(Power Devices)

核心技术:

-

SiC MOSFET选型:10kV级高压SiC器件的耐压等级、导通电阻(Rds(on))、开关损耗权衡

-

GaN HEMT应用:中低压高频场景(<1kV)的MHz级开关频率设计

-

驱动电路设计:高dv/dt(>50kV/μs)下的隔离驱动、米勒钳位、短路保护

-

串并联均压:多器件串联时的动态均压电路(TVS+RC缓冲)

技术挑战:SiC器件在10kV高压、50kHz高频工况下的长期可靠性(>10万小时),需考虑宇宙射线单粒子效应(SEE)、栅氧退化、体二极管双极退化。

2. 高频磁性元件设计(Magnetics)

核心技术:

-

磁芯材料选型:纳米晶合金(1K107B)vs 非晶合金(2605SA1)vs 铁氧体(Mn-Zn)

-

高频损耗建模:Steinmetz方程修正、Dowell效应(趋肤+邻近效应)计算

-

绝缘结构设计:高频方波(10-50kHz)下的电树枝化抑制、局部放电(PD)<10pC

-

热-磁耦合:磁芯损耗(Pcore)与绕组损耗(Pcu)的热反馈效应

技术挑战:高频工况下绝缘材料寿命比工频降低10倍,需采用聚酰亚胺(PI)薄膜+凡立水真空浸渍工艺。

3. 多电平拓扑与调制策略(Topology & Control)

核心技术:

-

拓扑选择:级联H桥(CHB)vs 模块化多电平(MMC)vs 双有源桥(DAB)

-

调制算法:SPWM、SVPWM、载波移相(CPS-SPWM)、最近电平逼近(NLM)

-

均压控制:子模块电容电压均衡(排序法、环流注入法)

-

故障容错:N+X冗余控制、子模块旁路(SM Bypass)算法

技术挑战:10kV直挂电网需数十个子模块串联,控制周期<100μs,需FPGA实现纳秒级同步。

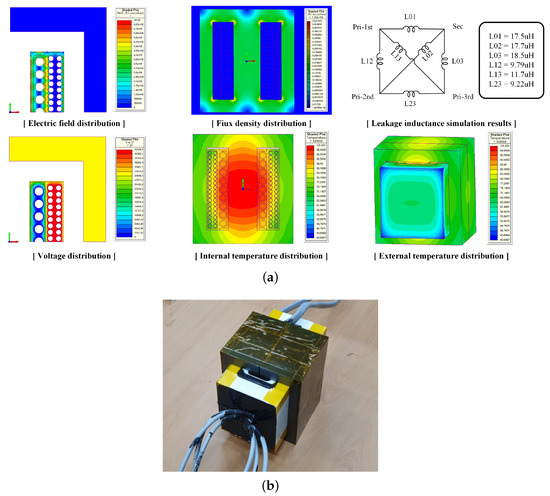

4. 多物理场耦合仿真(Multi-Physics)

核心技术:

-

电磁场:高频漏磁分布、涡流损耗(Eddy Current)、绝缘电场强度(Emax<3kV/mm)

-

热管理:IGBT/SiC结温(Tj<150℃)、磁芯热点、散热器CFD优化

-

结构力学:短路电动力(>100kA峰值)、振动噪声(<65dB)、热循环疲劳

-

绝缘失效:电-热-机械多场耦合下的绝缘老化预测

技术挑战:单个子模块仿真模型含>1000个元器件,整机系统需考虑模块化间的电磁干扰(EMI)。

5. 控制与通信系统(Control & Communication)

核心技术:

-

分层控制:站级(Station)-阀级(Valve)-子模块(SM)三级控制架构

-

通信协议:光纤通信(Avago HFBR系列)、IEEE 1588精确时间协议(PTP)

-

故障诊断:基于小波变换的故障特征提取、AI预测性维护

-

并网控制:虚拟同步机(VSG)、低电压穿越(LVRT)、谐波抑制(APF)

二、SST研发软件工具链

针对上述技术领域,SST研发需要构建完整的软件工具链:

电路与系统级仿真(Circuit/System Level)

| 软件 | 用途 | 核心功能 |

|---|---|---|

| MATLAB/Simulink | 控制算法开发 | 矢量控制、均压算法、故障容错策略建模 |

| PLECS | 电力电子系统仿真 | 热-电联合仿真、SiC/GaN器件库、多电平拓扑 |

| PSIM | 开关电路仿真 | 开关损耗计算、C代码自动生成、DSP验证 |

| LTspice | 细节电路验证 | 驱动电路、缓冲电路、RC吸收参数优化 |

电磁与多物理场仿真(Field Level)

| 软件 | 用途 | 核心功能 |

|---|---|---|

| Ansys Maxwell | 电磁场分析 | 高频变压器漏感、涡流损耗、绝缘电场分布 |

| COMSOL Multiphysics | 多物理场耦合 | 电磁-热-结构耦合、电树枝化模拟、PD检测 |

| JMAG | 电机/变压器设计 | 磁饱和分析、铁损计算、绕组趋肤效应 |

| Ansys Icepak | 热管理 | 散热器优化、风道CFD、结温预测 |

| Ansys Mechanical | 结构强度 | 短路电动力、振动模态、热应力分析 |

PCB与硬件设计(Hardware Design)

| 软件 | 用途 | 核心功能 |

|---|---|---|

| Altium Designer | 原理图/PCB设计 | 多层板(12-20层)、高速信号完整性、规则检查 |

| Cadence Allegro | 高端PCB设计 | 高功率密度布局、热过孔优化、EMC设计 |

| Ansys SIwave | 信号/电源完整性 | 高频PCB的PDN阻抗、串扰分析 |

控制实现与验证(Implementation)

| 软件 | 用途 | 核心功能 |

|---|---|---|

| TI Code Composer | DSP编程 | C2000系列DSP控制代码开发 |

| Xilinx Vivado | FPGA开发 | 调制算法硬件实现、光纤通信IP核 |

| dSPACE | HIL测试 | 硬件在环仿真、控制器验证 |

三、SST研发算力需求分析

SST仿真的计算特点极具挑战性:

-

多尺度问题:开关瞬态(ns级)与热时间常数(min级)跨度达10^9,需分层仿真

-

多物理场耦合:电磁-热-机械三场双向耦合,矩阵规模>1000万自由度

-

参数化扫描:需对开关频率、磁芯材料、散热条件进行DOE优化(>1000组工况)

-

实时性要求:HIL仿真需<10μs步长,对CPU实时性要求极高

四、UltraLAB硬件配置方案

基于SST研发的技术特点,推荐以下配置方案:

配置A:电力电子与控制算法开发工作站

定位:Simulink/PLECS电路仿真、控制算法开发、C代码生成

| 组件 | 规格 | 选型理由 |

|---|---|---|

| CPU | Intel Core i9-14900K (24核@6.0GHz) | 高频单核性能加速开关电路仿真(需小步长迭代) |

| 内存 | 64GB DDR5-6000 | 大型电力电子模型(>1000个子模块)载入 |

| 存储 | 2TB NVMe Gen4 + 8TB SATA | 系统盘+仿真数据/文献库 |

| GPU | RTX 4070 12GB | 加速Simulink可视化、深度学习控制算法训练 |

| 外设 | 双27寸4K显示器 | 左屏Simulink模型,右Scope波形观察 |

| 扩展 | 高速USB3.0×6 | 连接JTAG调试器、示波器、功率分析仪 |

软件环境:预装MATLAB R2024b+Simulink+Simscape Electrical+PLECS+TI C2000支持包

配置B:电磁-热多物理场仿真工作站

定位:Maxwell/COMSOL高频变压器电磁-热耦合仿真、绝缘设计验证

| 组件 | 规格 | 选型理由 |

|---|---|---|

| CPU | Intel Xeon W9-3495X (56核@4.8GHz) | Maxwell涡流求解器支持多核并行,56核加速3D电磁场计算 |

| 内存 | 512GB DDR5-5600 ECC | 高频变压器3D模型(含气隙、绕组细节)网格>500万单元,需大内存 |

| GPU | RTX pro5000 72GB | 加速Maxwell 3D场显示、支持GPU加速的涡流求解 |

| 存储 | 4TB NVMe Gen5 (14GB/s) | 快速保存大规模场数据(单文件>10GB) |

| 显示器 | 双32寸4K专业显示器 | 大尺寸模型细节观察 |

| 网络 | 10GbE | 与团队共享大型仿真文件 |

特色优化:预装Ansys Maxwell 2024、COMSOL 6.3,配置多物理场耦合求解环境

配置C:系统级多物理场集群(整机系统仿真)

定位:整机SST系统(10kV/6MW)的电磁-热-结构耦合、模块化冗余仿真

| 组件 | 规格 | 选型理由 |

|---|---|---|

| 架构 | 双路AMD EPYC 9684X (96核×2) | 192核支持大规模并行,适合整机等效电路仿真 |

| 内存 | 2TB DDR5-4800 | 整机系统含数百个子模块,瞬态仿真需加载大量状态变量 |

| GPU | A100 80GB ×2 | 大规模CFD热仿真、整机电磁场可视化 |

| 存储 | 30TB NVMe RAID 0 (28GB/s) | 支持参数化扫描(DOE)快速写入数百组结果 |

| 网络 | InfiniBand HDR (200Gb/s) | 多节点并行计算时数据同步 |

适用场景:整机能效优化、故障容错策略验证、短路电动力计算

配置D:HIL测试与实时仿真平台

定位:控制器硬件在环(HIL)测试、FPGA实时仿真

| 组件 | 规格 | 选型理由 |

|---|---|---|

| 实时系统 | dSPACE SCALEXIO或Speedgoat | 支持<1μs步长的电力电子实时仿真 |

| CPU | Intel Core i7-14700K (实时内核) | 硬实时性能,无抖动 |

| FPGA | Xilinx Kintex-7/Virtex-7 | 纳秒级调制算法实现、多路光纤通信 |

| I/O | 高速ADC/DAC (≥10MS/s) | 模拟量采集与输出 |

| 隔离 | 光耦隔离+屏蔽机箱 | 10kV高压测试安全防护 |

特色:预装dSPACE ConfigurationDesk或Speedgoat Simulink Real-Time Target

五、SST研发工作流最佳实践

基于上述软硬件配置,建议采用以下研发流程:

阶段1:拓扑与参数设计(配置A)

-

Simulink搭建平均模型(Average Model),验证控制策略

-

PLECS进行开关级仿真,优化调制策略与均压算法

-

输出关键参数(开关频率、磁芯规格、散热需求)

阶段2:磁性元件设计(配置B)

-

Maxwell进行3D电磁场仿真,优化绕组布局降低漏感

-

COMSOL进行电-热耦合,验证绝缘材料温升与电场分布

-

Icepak进行散热器CFD优化,确保SiC结温<125℃

阶段3:整机系统集成(配置C)

-

构建整机等效电路模型,进行故障容错策略验证

-

多物理场耦合仿真:短路工况下的电动力+热冲击+绝缘应力

-

参数化扫描优化:开关频率vs效率vs体积的帕累托前沿

阶段4:控制器验证(配置D)

-

HIL测试:控制器+实时仿真器闭环,验证极端工况

-

FPGA代码生成:自动部署到实际控制器

-

型式试验:高压绝缘、温升、短路、EMC测试

六、总结:算力即创新速度

固态变压器的研发是一场"材料-器件-拓扑-控制"的多维博弈。在10kV高压、50kHz高频、兆瓦功率的极端工况下,任何设计疏忽都可能导致绝缘击穿或器件炸管。高性能仿真不是可选项,而是降低研发成本、缩短上市周期的核心手段。

一台配置得当的UltraLAB工作站,可以将:

-

高频变压器电磁设计周期从4周压缩至1周

-

多物理场耦合仿真从"无法完成"变为" overnight运行"

-

控制算法迭代从"试制-炸机-返修"变为"HIL虚拟验证"

当SiC器件价格年降42%,当SST市场暴涨217%,唯有掌握先进仿真工具与算力底座的团队,才能在这场能源革命中抢占先机。

延伸阅读:如需了解SST特定拓扑(DAB/MMC/CHB)的详细仿真设置,或SiC器件损耗建模参数,可联系UltraLAB技术团队获取《固态变压器多物理场仿真白皮书》及样机配置模板。

这篇软文紧扣SST研发的技术难点(高压绝缘、高频磁性、模块化控制),给出了从电路仿真到多物理场耦合的完整软件链,以及对应UltraLAB配置方案。如需调整侧重(如更偏向电网级SST或车载SST),或补充具体仿真案例(如DAB变换器损耗分析),请随时告诉我。

UltraLAB图形工作站供货商:

西安坤隆计算机科技有限公司

国内知名高端定制图形工作站厂家

业务电话:400-705-6800

咨询微信号:100369800

上一篇:没有了